A standard 24-transistor implementation of a static 1-bit full

5 (745) In stock

5 (745) In stock

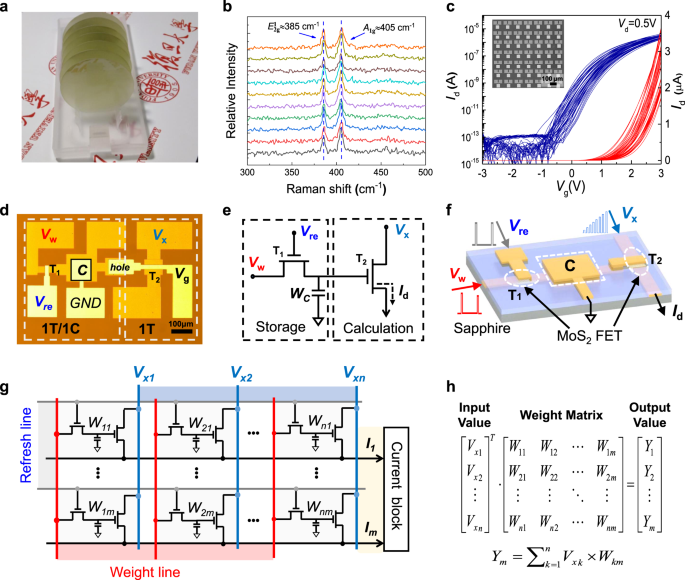

An in-memory computing architecture based on two-dimensional semiconductors for multiply-accumulate operations

Spectrum R of a four variable completely specified Boolean function.

1 bit Full adder transistor level implementation using Complementary Pass transistor logic

PDF) Reducing the number of transistors in digital circuits using gate-level evolutionary design

Proposed 1-bit adder circuit 2 using pass-transistor and transmission

Compact implementation of F05: (A ⊕ B) · C. Any combination of

A standard 24-transistor implementation of a static 1-bit full adder

CMOS full adder cells based on modified full swing restored complementary pass transistor logic for energy efficient high speed arithmetic applications - ScienceDirect

A standard 24-transistor implementation of a static 1-bit full adder

Mirror full adder schematic [4]

Impact of multi threshold transistor in positive feedback source coupled logic (PFSCL) fundamental cell

Low-Power and Fast-Swing-Restoration GDI-Based Magnitude Comparator for Digital Images Processing